# The ALICE TPC Front End Electronics

L. Musa\*, J. Baechler <sup>a</sup>, N. Bialas <sup>b</sup>, R. Bramm <sup>a,b</sup>, R. Campagnolo <sup>a</sup>, C. Engster <sup>a</sup>, F. Formenti <sup>a</sup>, U. Bonnes <sup>c</sup>, R. Esteve Bosch <sup>a</sup>, U. Frankenfeld <sup>d</sup>, P. Glassel <sup>e</sup>, C. Gonzalez <sup>a</sup>, H.-A. Gustafsson <sup>f</sup>, A.

Jimenez<sup>a</sup>, A. Junique<sup>a</sup>, J. Lien<sup>g</sup>, V. Lindenstruth<sup>h</sup>, B. Mota<sup>a</sup>, P. Braun-Munzinger<sup>d</sup>, H. Oeschler<sup>c</sup>, L. Osterman<sup>f</sup>, R. Renfordt<sup>b</sup>, G. Rüschmann<sup>b</sup>, D. Rohrich<sup>g</sup>, H.-R. Schmidt<sup>d</sup>, J. Stachel<sup>e</sup>, A.-K. Soltveit<sup>c</sup>, K. Ullaland<sup>g</sup>

Abstract— In this paper we present the Front End Electronics for the Time Projection Chamber (TPC) of the ALICE experiment. The system, which consists of about 570000 channels, is based on two basic units: (a) an analogue ASIC (PASA) that incorporates the shaping-amplifier circuits for 16 channels; (b) a mixed-signal ASIC (ALTRO) that integrates 16 channels, each consisting of a 10-bit 25-MSPS ADC, the baseline subtraction, tail cancellation filter, zero suppression and multi-event buffer. The complete readout chain is contained in Front End Cards (FEC), with 128 channels each, connected to the detector by means of capton cables. A number of FECs (up to 25) are controlled by a Readout Control Unit (RCU), which interfaces the FECs to the Data Acquisition (DAQ), the Trigger, and the Detector Control System (DCS). A fraction of the final electronics (1024 channels) has been characterized in a test that incorporates a prototype of the ALICE TPC as well as many other components of the final set-up. The tests show that the system meets all design requirements. Originally conceived and optimized for the Time Projection Chamber (TPC) of the ALICE experiment, its architecture and programmability make this system suitable for the readout of a wider class of detectors.

#### INTRODUCTION I.

ALICE [1] (A Large Ion Collider Experiment), currently in preparation for initial operation in 2007, is dedicated to the study of the collisions at relativistic energies of several species of ions. The high energy ions collisions at LHC will have an extremely high particle multiplicity. For the central events in Pb-Pb running, for instance, about  $3 \times 10^4$  charged particles will be produced in the detector acceptance. The experimental apparatus to study the high number of particles produced in each collision, is a multi-component detector. An important role in the ALICE detector is played by the Time Projection Chamber [2] (TPC), which provide a three-dimensional reconstruction of the particle trajectories. The ALICE TPC consists of a cylindrical gas volume (about 90 m<sup>3</sup> of Ne-CO<sub>2</sub>), divided in two drift regions by a high voltage plane located at its axial centre, under a uniform electrostatic field. Charged particles traversing the TPC volume ionise the gas along their path liberating electrons that drift towards the chamber endplates. At the endplates, conventional Multi-Wire Proportional Chambers provide the charge amplification and readout by means of a cathode plane segmented in about  $5.7 \times 10^{\circ}$  pads. In the MWPC the signal released on the pads is characterised by a fast rise time (less than 1 ns) and a long tail. The amplitude has a typical value of 7  $\mu$ A. The signal is delivered on the detector impedance that, to a very good approximation, is a pure capacitance of the order of few pF. The shape of the signal tail is rather complex and depends on the detail of the chamber and pad geometry. This tail, causing pile-up effects, sets the main limitation to the maximum track density at which a MWPC can be operated. Therefore, an accurate tail cancellation and baseline restoration of the detector signal are fundamental requirements for the front-end electronics design, especially if data compression has to be performed on-line before shipping the data off detector. Indeed, the TPC will be operated at a maximum trigger rate of 200 Hz in Pb-Pb running and 1 kHz in p-p running, producing respectively 142 GByte/s and 710 GByte/s of uncompressed data.

#### II. GENERAL REQUIREMENTS

The main requirements for the readout electronics are listed in Table I. One of the tightest requirements is defined by the extremely high pulse rate with which the ALICE TPC FEE has to cope. Indeed, the detector innermost chamber will be exposed to signal occupancy up to 50%. On the other hand, the extremely large data volume (~ 700 MByte/event) requires performing the zero suppression in the FEE. Therefore, in order to preserve the full resolution on the signal features (amplitude and time), a very accurate cancellation of the signal tail and correction of the baseline have to be performed before the zero suppression.

The radiation load on the TPC is low (1krad  $\oplus$  10<sup>11</sup> neutrons/cm<sup>2</sup> over 10 years). Thus standard radiation-soft

Manuscript received Nov 14, 2003.

<sup>\*</sup> Luciano Musa, corresponding author, is with CERN, Geneva, CH-1211 Switzerland, (telephone: +41-22-7676261, e-mail: luciano@cern.ch).

Authors with CERN, Geneva, CH12-11 Switzerland.

<sup>&</sup>lt;sup>b</sup> Authors with Institute für Kernphysik, Johann-Wolfgang-Universität, Frankfurt, Germany.

Authors with Institut für Kernphysik, Technische Universität Darmstadt, Germany.

Authors with GSI, Darmstadt, Germany.

Authors with Physikalisches Institut, Ruprecht-Karls-Universität, Heidelberg, Germany.

Authors with Division of High Energy Physics, University of Lund, Sweden.

Authors with University of Bergen, Bergen, Norway.

<sup>&</sup>lt;sup>h</sup> Authors with Kirchhoff\_Institut für Physik, Ruprecht-Karls-Universität, Heidelberg, Germany.

technologies are suitable for the implementation of this electronics. However, some special care should be taken to protect the system against potential damages caused by Single Event Effects.

TABLE I FRONT END ELECTRONICS REQUIREMENTS

| PARAMETER                   | VALUE                 |

|-----------------------------|-----------------------|

| Nr. of channels             | 557 568               |

| Signal-to-noise ratio (MIP) | 30:1                  |

| Dynamic range               | 900:1                 |

| Noise (ENC)                 | < 1000 e <sup>-</sup> |

| Conversion gain             | 6 ADC counts / fC     |

| Cross-talk                  | < 0.3 %               |

| Shaping time (FWHM)         | 190 ns                |

| Sampling rate               | 5 – 12 MHz            |

| Tail suppression after 1µs  | 1%0                   |

| Power consumption           | < 100 mW / channel    |

The front-end electronics system has to satisfy many other constraints while meeting the required performance specifications. Mainly, the read-out electronics needs to fit into the overall detector structure; in particular into the available space, which has important consequences for the requirements on reliability, power, and cooling.

## III. SYSTEM OVERVIEW

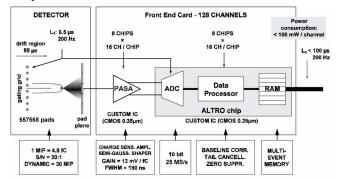

A single readout channel is comprised of three basic functional units (Fig. 1): a charge sensitive amplifier/shaper (PASA); a 10-bit 25-MSPS low power ADC; a digital circuit that contains a shortening filter for the tail cancellation, the baseline subtraction and zero suppression circuits, and a multiple-event buffer.

Fig. 1. An overview of the ALICE TPC front end electronics.

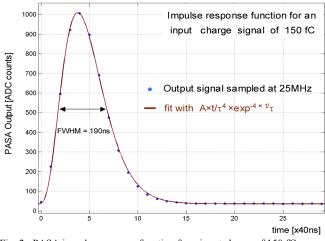

The charge collected at the TPC pads is amplified and integrated by a low input impedance amplifier. It is based on a charge sensitive amplifier (CSA) followed by a semi-Gaussian pulse shaper of the 4<sup>th</sup> order. These analogue functions are realised by a custom integrated circuit, implemented in the AMS CMOS 0.35  $\mu$ m technology, which contains 16 channels with a power consumption of 11 mW/channel. The circuit has a conversion gain of 12 mV/fC and an output dynamic range of 2 V with a differential non-linearity of 0.2%. It produces a pulse (Fig. 2) with a shaping time (FWHM) of 190 ns. The single channel has a noise value below 570 e<sup>-</sup> (r.m.s.) and a channel-to-channel cross–talk below -60 dB.

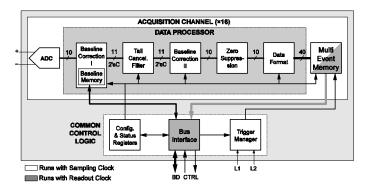

Immediately after the PASA, a 10-bit pipelined ADC (one per channel) samples the signal at a rate in the range 5 to 12 MHz. The digitised signal is then processed by a set of circuits that perform the baseline subtraction, tail cancellation, zero-suppression, formatting and buffering. The ADC and the digital circuits are contained in a single chip named ALTRO [3,4]. ALTRO (see Fig. 3) integrates 16 channels, each of them consisting of a 10-bit, 25-MSPS ADC, a pipelined Digital Processor and a multi-acquisition Data Memory.

Fig. 2. PASA impulse response function for a input charge of 150 fC.

When a Level-1 trigger is received a predefined number of samples (acquisition) is temporarily stored in a data memory. Upon Level-2 trigger arrival the latest acquisition is frozen, otherwise it will be overwritten by the next acquisition. The Digital Processor, running at the sampling frequency, implements several algorithms that are used to condition and shape the signal. After digitization, the Baseline Correction Unit I is able to perform channel-to-channel gain equalization and to correct for possible non-linearity and baseline drift of the input signal. It is also able to adjust DC levels and to remove systematic spurious signals by subtracting a pattern stored in a dedicated memory. The next processing block is an 18-bit, fixed-point arithmetic, 3<sup>rd</sup> order Tail Cancellation Filter. The latter is able to suppress the signal tail, within 1 µs after the pulse peak, with the accuracy of 1 LSB. Since the coefficients of this filter are fully programmable, the circuit is able to cancel a wide range of signal tail shapes. Moreover, these coefficients can be set independently for each channel and are re-configurable. This feature allows a constant quality of the output signal regardless of ageing effects on the detector and/or channel-to-channel fluctuations. The subsequent processing block, Baseline Correction Unit II, applies a baseline correction scheme based on a moving average filter. This scheme removes non-systematic perturbations of the baseline that are superimposed to the signal. At the output of this block, the signal baseline is constant with an accuracy of 1 LSB. Such accuracy allows an efficient Zero-Suppression procedure, which discards all data below a programmable threshold, except for a specified number of pre- and post-samples around each pulse.

Fig. 3. Block diagram of the ALTRO chip.

This produces a certain number of non-zero data packets, thus reducing the overall data volume. Each data packet is formatted with its time stamp and size information in a way that reconstruction is possible afterwards. The output of the Data Processor is sent to a Data Memory of 5 Kbyte, able to store up to 8 full acquisitions.

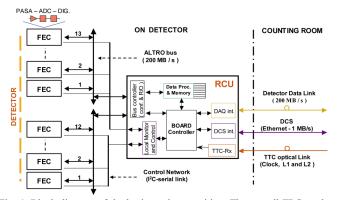

Fig. 4. Block diagram of the basic readout partition. The overall TPC readout consists of 216 readout partitions.

The data can be read out from the chip at a maximum speed of 60 MHz through a 40-bit wide bus, yielding a total bandwidth of 300 Mbyte/s. Moreover, the readout speed and the ADC sampling frequency are independent. Therefore, the readout frequency does not depend on the bandwidth of the input signal being acquired. The ALTRO chip is implemented in the STMicroelectronics CMOS 0.25 µm technology.

The complete readout chain is contained in the Front End Cards (FEC), which are plugged in crates attached to the detector mechanical structure. Each FEC contains 128 channels and is connected to the cathode plane by means of 6 flexible cables. A number of FECs (up to 25) are controlled by a Readout Control Unit (RCU) [5]. As sketched in Fig. 4, the RCU interfaces the FECs to the DAQ, the Trigger, and the

Detector Control System. The RCU broadcasts the trigger information to the individual FEC modules and controls the readout procedure. Both functions are implemented via a custom bus, based on low-voltage signaling technology (GTL), the ALTRO bus.

#### IV. THE FRONT END CARD

The Front-End Card (FEC) contains the complete read-out chain for the amplification, shaping, digitisation, processing and buffering of the TPC signals; it must handle the signal dynamic range of about 10 bits with minimal degradation of precision and store the signals during the Level-2 trigger latency.

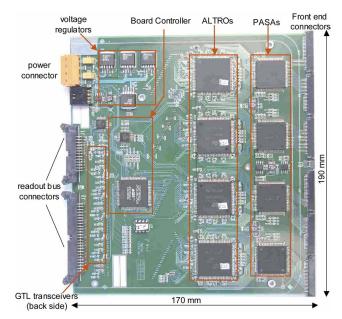

Fig. 5. FEC layout. The components are mounted on both sides of the board. The figure shows the board topside with 4PASAs, 4 ALTROS, 1 FPGA, the voltage regulators and some other minor components. On the bottom side are placed the other 4 PASAs and 4 ALTROs and, close to the readout bus connectors, the GTL transceivers.

With reference to Fig. 5, we describe hereafter the FEC layout following the signals flow. The FEC receives 128 analogue signals through 6 flexible kapton cables and the corresponding connectors. The input signals are very fast, with a rise time of less than 1ns. Therefore, to minimise the channel-to-channel crosstalk, the 8 PASA circuits have to be very close to the input connectors. The analogue to digital conversion and the digital processing are done by the ALTROs, which are connected to the corresponding PASAs with differential signals. It should be noticed that the PASA and ALTRO can also be interconnected in a single-ended mode. However, the noise increases by a factor two with respect to the differential-mode interconnection adopted in the FEC.

The FEC channels are multiplexed, at the board level, through a LVCMOS bus. It features an asynchronous VME-like protocol, which is enhanced by a clocked block-transfer that provides a bandwidth of up to 300 Mbytes/s. The FEC is interfaced to the RCU through a bus based on the GTL technology, named ALTRO bus. At the board output the bus signals are translated from LVCMOS level to GTL level by bidirectional transceivers. The configuration, readout and test of the board are done via the GTL bus. Moreover, the FEC contains a circuit implemented in a FPGA, named Board Controller (BC), which provides the RCU with an independent access to the FEC via an  $I^2C$  link. This secondary access is normally used to control the state of the voltage regulators and monitor the board activity, power supplies and temperature.

Fig. 6. Copper cooling plates and FEC assembly.

The board offers a number of test facilities. As an example a data pattern can be written in the ALTRO chip and readout back exercising the complete readout chain. The Board Controller allows verifying the bus activities, the presence of the clock and the number of triggers received.

The ALTRO chips and the BC work synchronously under the master clock with a frequency up to 60 MHz. The ALTRO circuits usually perform the same operations concurrently, under the control of the RCU. However, the latter can also control a single channel at a time. This is performed in the configuration phase and for test purposes. The RCU broadcasts the trigger information to the individual FEC modules and controls the readout procedure. Both functions are implemented via the GTL bus.

In order to match the position of the connectors on the back of the chamber pad plane, the FEC has a width of 190 mm. Moreover, in order to fit into the available space its height and thickness are of 170 mm and 14 mm respectively.

The FEC printed circuit board (PCB) contains 4 signal layers and 4 power layers (2 supply layers with the corresponding ground layers). The power layers have essentially the same geometry. The duplication of the power and ground layers, provides the following advantages: 1) it eases the implementation of controlled-impedance lines; 2) it reduces the voltage drop over the power layers; 3) it reduces the noise produced by the ground bouncing. From the power supply point of view the board is divided in three main sections: the PASA section, the ALTRO/ADC section and the digital section. Therefore each power layer consists of three different power planes. The ALTRO/ADC and the digital planes are supplied with the same input voltage (+2.5 V), and are closed together at the input of the voltage regulators. The PASA plane is supplied at +3.3 V. The three ground planes (PASA ground, ALTRO/ADC ground and digital ground) are closed together with a pad, which is located upstream the voltage regulators.

The FEC has a maximum power consumption of about 6 W. In order to minimize the heat transfer to the detector sensitive volume, the FECs are embedded in two copper plates cooled by water (see Fig. 6).

#### V. SYSTEM PERFORMANCE

A fraction of the final electronics (1024 channels) has been characterized in a test that incorporates a prototype of the ALICE TPC as well as many other components of the final setup (e.g. detector data link, cooling system and low-voltage power supply).

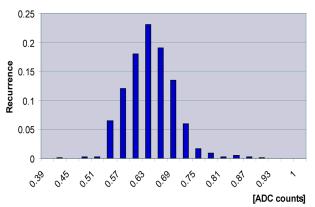

Fig. 7. Histogram of the r.m.s. noise for 1024 FEC channels connected to the detector.

As ionization sources the <sup>83</sup>Kr radioactive decay and cosmic rays have been used. The tests show that the system meets all design requirements. It exhibits a noise (r.m.s.) of 0.65 ADC counts (Fig. 7), which corresponds to an equivalent noise charge of 730 e, and a spread in the output DC level of 3% of the dynamic range.

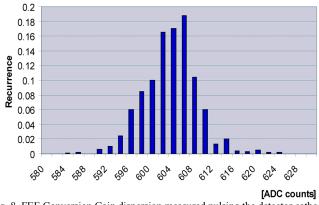

The dispersion of the conversion gain has been measured pulsing the detector chamber cathode wires. The resulting pulse height distribution shows a dispersion in the overall signal conversion gain of the order of 8 ADC counts (r.m.s.) (Fig. 8).

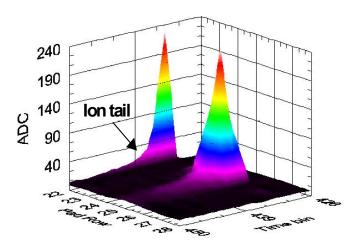

Particular emphasis was given to the detailed characterization of the detector signal and the study of the performance of the digital processing algorithms. The study of single ionization clusters (Fig. 9), produced by the decay of the <sup>83</sup>Kr, allowed a full characterization of the signal ion tail and the calculation of the coefficients of the tail cancellation filter.

Fig. 8. FEE Conversion Gain dispersion measured pulsing the detector cathode wires.

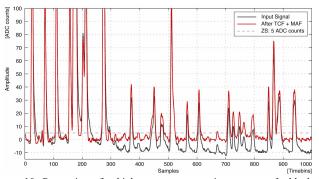

The detection of events produced by large showers of cosmic rays allowed testing the performance of the tail cancellation and baseline correction circuits. Indeed, a few events were characterized by the same signal occupancy (about 50%) predicted for the relativistic collisions of heavy ions in ALICE (Fig. 10).

Figure 9: Single ionization cluster produced by the decay of 83Kr.

These measurements show that the ALTRO chip performs a good cancellation of the signal tail (0.1% of the signal amplitude within 1  $\mu$ s) and the restoration of the baseline (within 1 ADC count), even for very high signal occupancy.

## VI. CONCLUSIONS

An innovative readout electronic system with on-detector signal processing has been developed for the ALICE TPC. A fraction of the final electronics has been benchmarked by realistic measurements with a prototype of the ALICE TPC.

Test show that the system fulfils all design requirements. In particular, despite of the high level of integration of digital circuits close to the analogue front-end, the system shows a noise figure of 730 e<sup>-</sup> (r.m.s.). Moreover, the tests have shown

that the system is able to process high multiplicity events with a baseline restoration at 1‰ of the dynamic range within 1  $\mu$ s. The average power consumption of the final system is about 40 mW/channel.

Figure 10: Processing of a high occupancy cosmic ray event. In black the signal at the input of the ALTRO chip processing chain. In red the combined effects of the ALTRO's Tail Cancellation filter. (TCF) and Moving Average filter (MAF). The dotted line represents the zero suppression threshold. The application of the TCF and MAF allows retrieving signals that otherwise would be discarded by the zero suppression algorithm.

#### VII. REFERENCES

- [1] ALICE Collaboration, "Technical Proposal", ISBN 92-9083-077-8, December 95, CERN, Geneva, Switzerland.

- [2] ALICE Collaboration, "A Large Ion Collider Experiment, ALICE TPC -Technical Design Report", ISBN 92-9083-155-3, December 1999, CERN, Geneva, Switzerland.

- [3] R. Esteve Bosch, A. Jimenez, B. Mota and L. Musa, "A Low-Power 16channel A/D Converter and Digital Processing ASIC", *Proc. of the ESSCIRC*, Florence, Italy, Sept. 2002.

- [4] R. Esteve Bosch, A. Jimenez, B. Mota and L. Musa, "The ALTRO Chip: A 16-channel A/D Converter and Digital Processor for Gas Detectors", *IEEE Transaction on Nuclear Science*, Vol. 50 No. 6, December 2003.

- [5] J.A.Lien et al., "Readout Control Unit of the Front end Electronics for the ALICE Time Projection Chamber", *Proceedings of the 8<sup>th</sup> Workshop* on *Electronics for LHC Experiments*, Colmar, France, 9-13 September 2002.