#### Front End Card - status report

#### Alice TPC Meeting, C.E.R.N. - 29/30 April 2002

Roberto Campagnolo – CERN Ep-Ed

presentation available at http://cern.ch/ep-ed-alice-tpc/

# OUTLINE

- The New Front End Card

- Related Interfaces

- new 40-bit Mezzanine,

- Termination/ Service card,

- Analog Test card

- Test and Measurements

- Conclusions

## Why a New Front End Card ?

The Old FEC Integrates :

- 8 PASA from CERES

- 64 discrete dual-channel ADC

- 16 ALTRO chip (4 channels prototype)

- 32 bit Read Out BUS

The New FEC Integrates :

- 8 Newest PASA

- 8 ALTRO –16 channels each

- 40 bit Read Out BUS

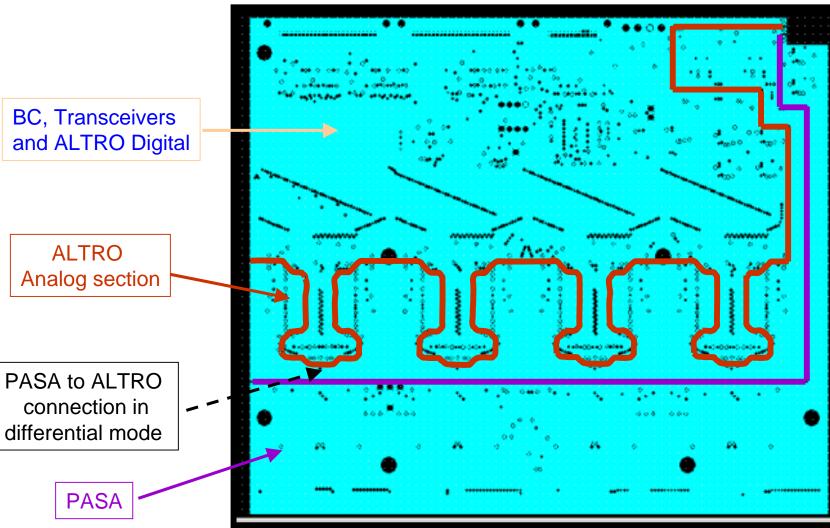

### **FEC - Circuit Board layout : The Ground plane**

ALTRO bus - RCU side

FRONT END CONNECTORS

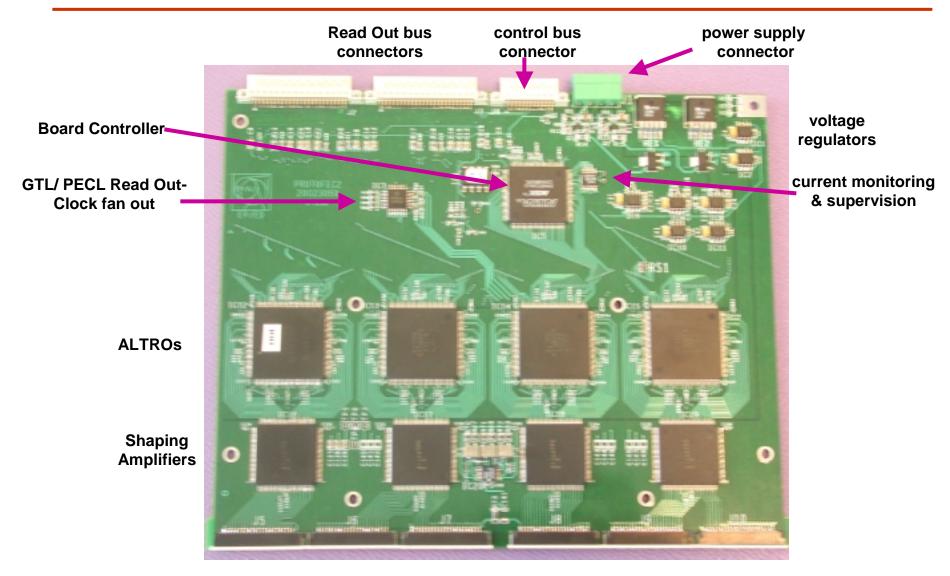

#### **The New Front End Card: TOP view**

**HARWIN** connectors

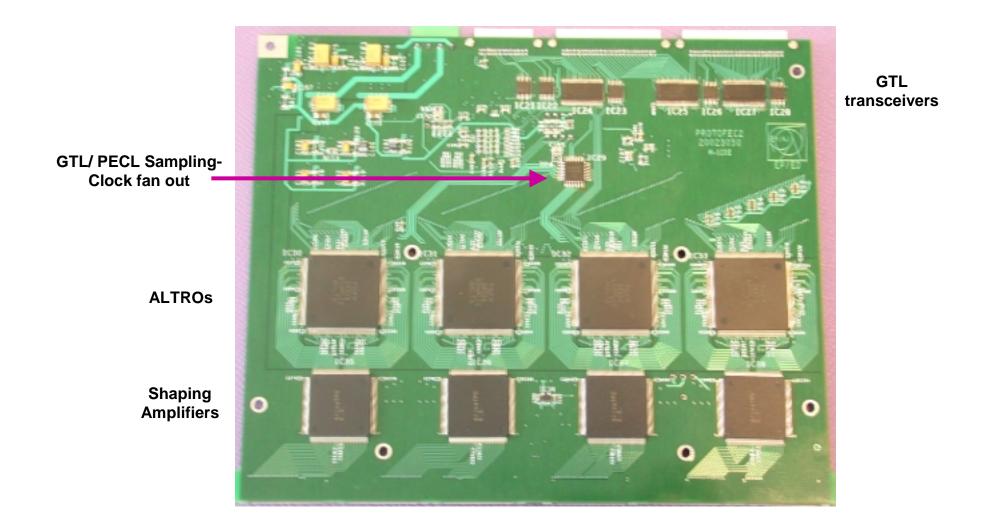

#### **The New Front End Card:Bottom view**

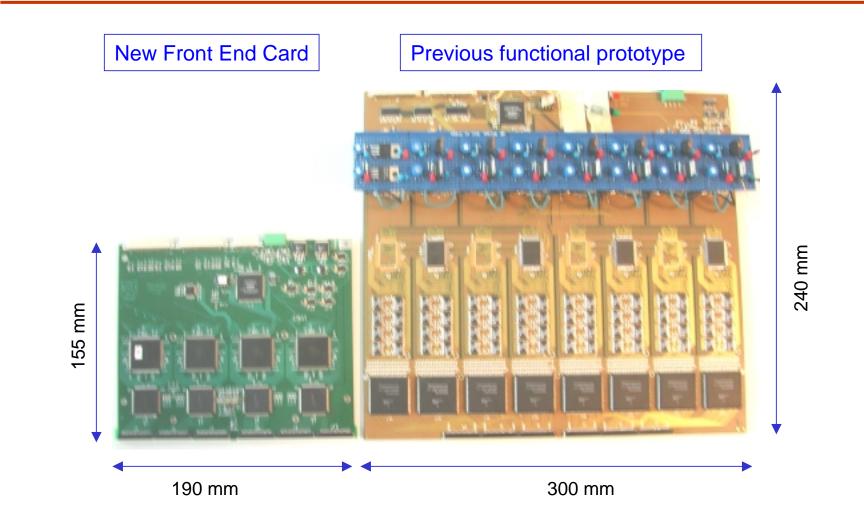

### **FECs – dimensional comparison**

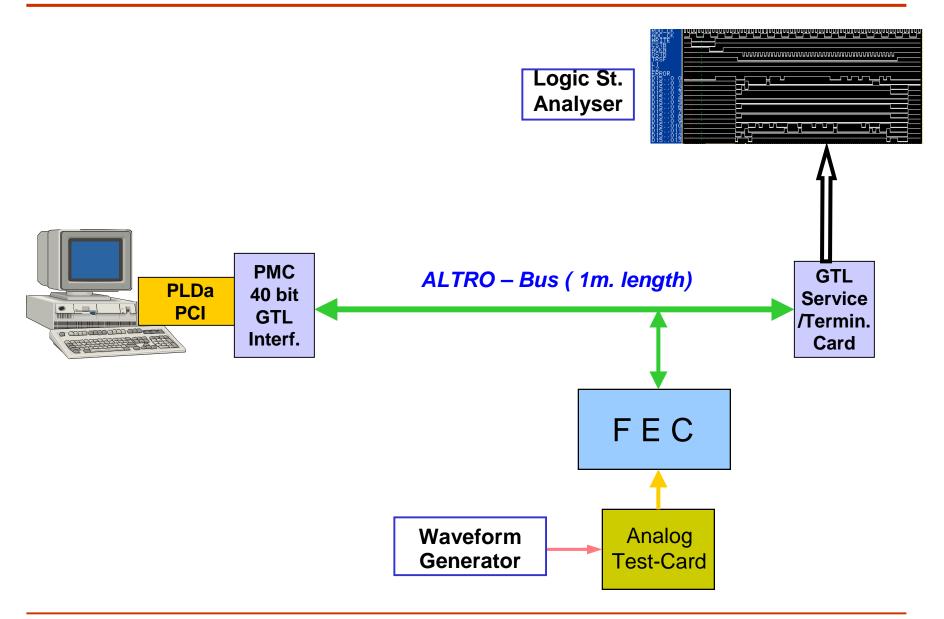

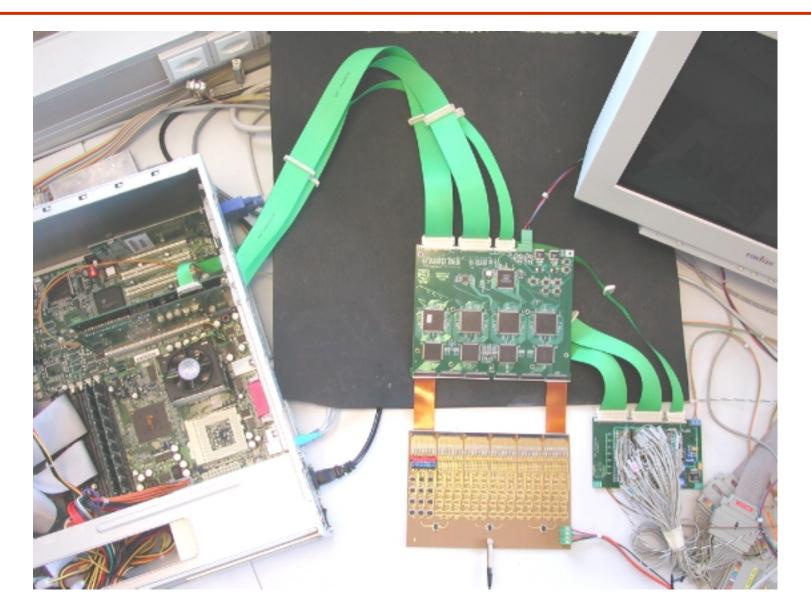

#### Front End Card - Test Set Up

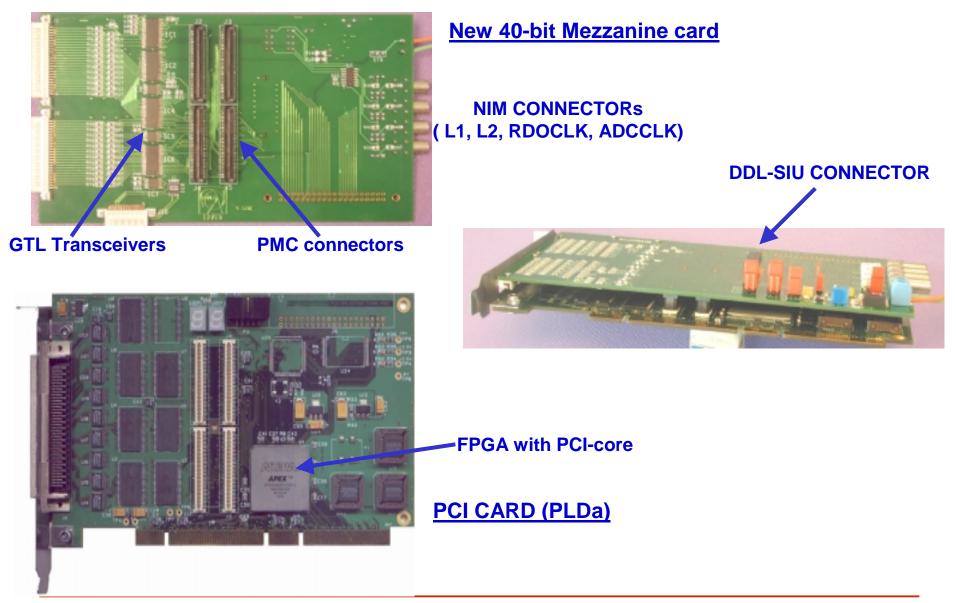

#### The new Mezzanine for PCI-based RCU

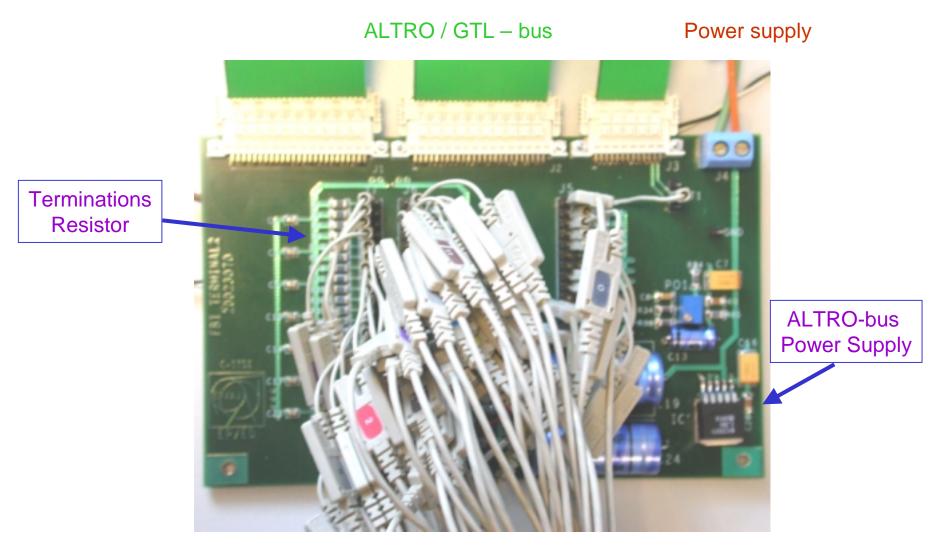

### The service card layout

Logic State Analyzer probes

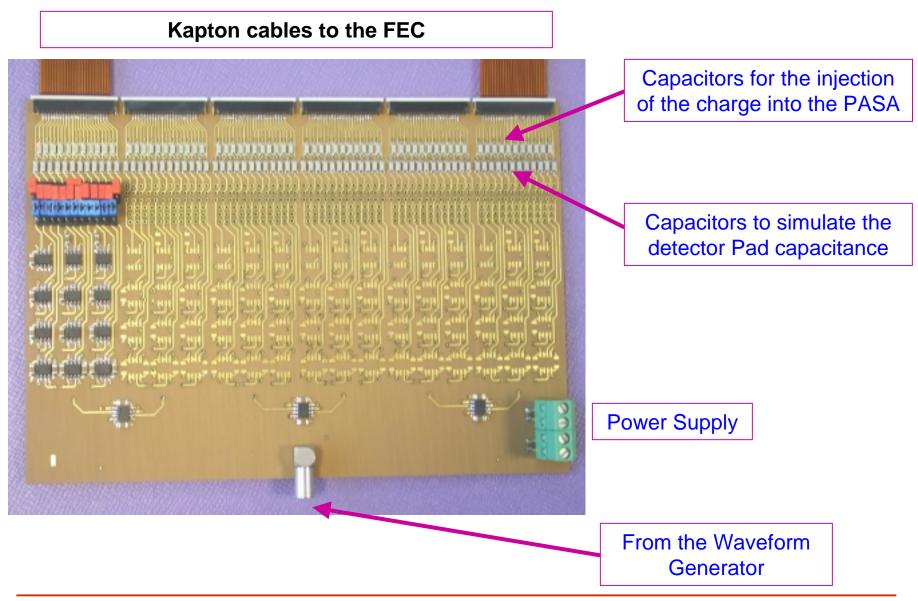

### **Analog Test Card layout**

### **Complete system overview**

### **Self Test results : variable pattern on 128 channels**

### **Communications with the FEC**

100/500MHz LA D Waveform 1 Acq. Control [Cancel D15..0 Accumulate Center X -> ABCD Off Screen Hex 0 -> ABCD Trig to O Delay Trig to X Markers X to O 516.0 ns 207.2 ns 723.2 ns 489.2 ns Time Access to an Altro Register (Write and Read) מטוטוטוטוטוטוטוט 1000PM 100/500MHz LA D Acq. Control Waveform 1 Cancel D35.20 Accumulate X -> 001A Center Off Screen Hex 0 -> FFFE Trig to X Trig to O Delay. Markers X to O 941.2 ns Time 2.601 us 92.00 ns 2.693 us Event download (Transfer) ٩Ū பா

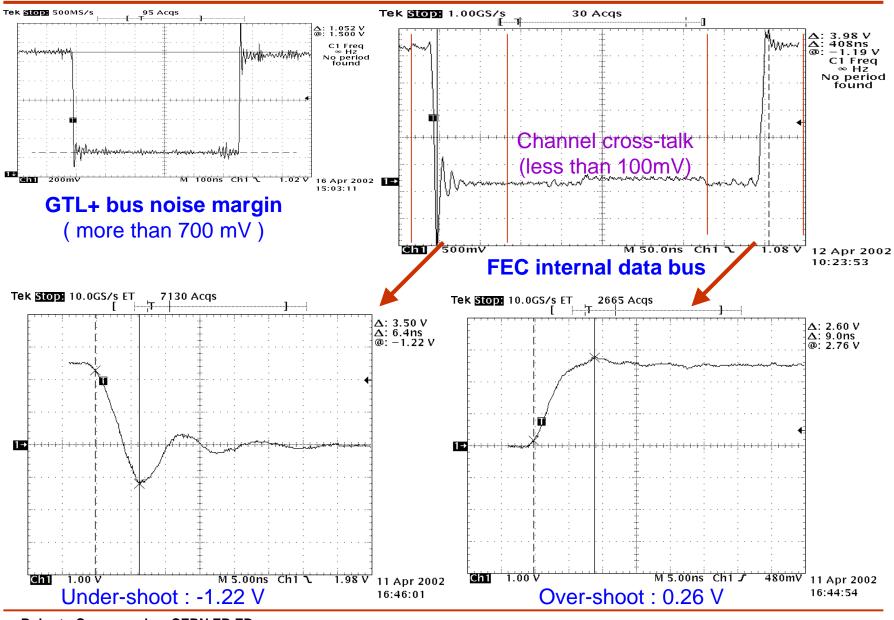

#### **GTL and internal bus Overall signal quality**

Roberto Campagnolo – CERN EP-ED

## **FEC Power Consumption**

| Board Controller :                                 | 140 mW    |

|----------------------------------------------------|-----------|

| <ul> <li>Slow control circuitry :</li> </ul>       | 5 mW      |

| <ul> <li>ADC and Read Out Clock fan-out</li> </ul> | :~ 500 mW |

| GTL transceivers :                                 | 60 mW     |

| • 8 ALTRO :                                        | ~ 2060 mW |

| • 8 PASA :                                         | ~ 1530 mW |

| <ul> <li>Polarization circuitry:</li> </ul>        | 7mW       |

• Power Regulators (20% avg. drop):~ 860 mW

TOTAL POWER CONSUMPTION : ~ 5200 mW => 40.5 mW / channel

Preliminary tests shown that the present version of Front end Card fully satisfies the requirements for the interface of the ALTRO chip to the read out bus.

Nevertheless the design features related to the analog section of the card ( PASA chips and related signals routing ) have still to be verified because of the logic for the read-out of events by the RCU is still under construction.