# FRONT END CARD

**ALICE TPC Meeting**

GSI (Darmstadt), December 11, 2001

### **OUTLINE**

- Summary of the prototyping activities

- New FEC design

- Future work

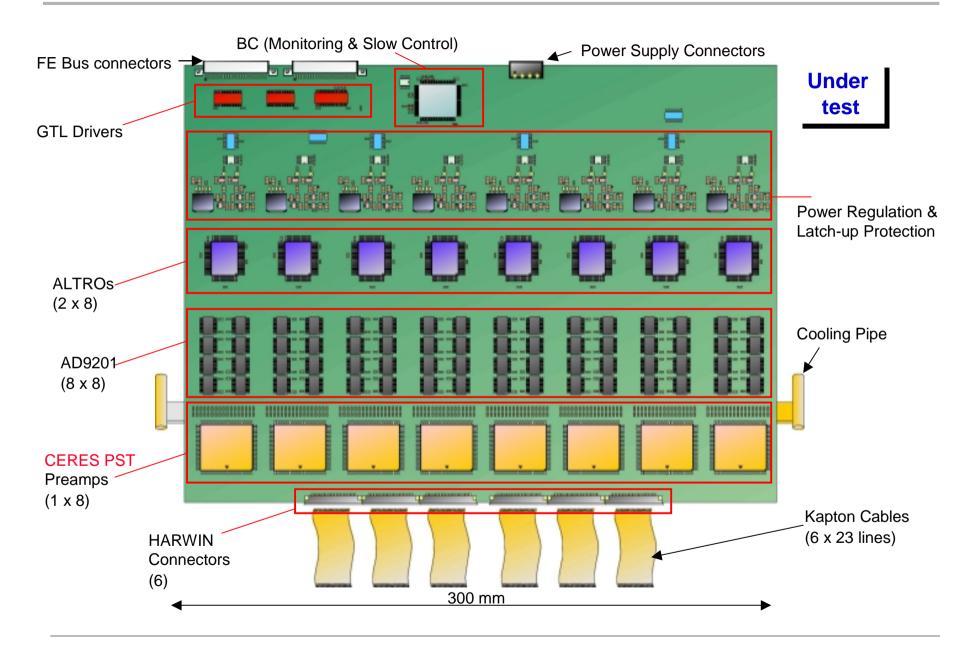

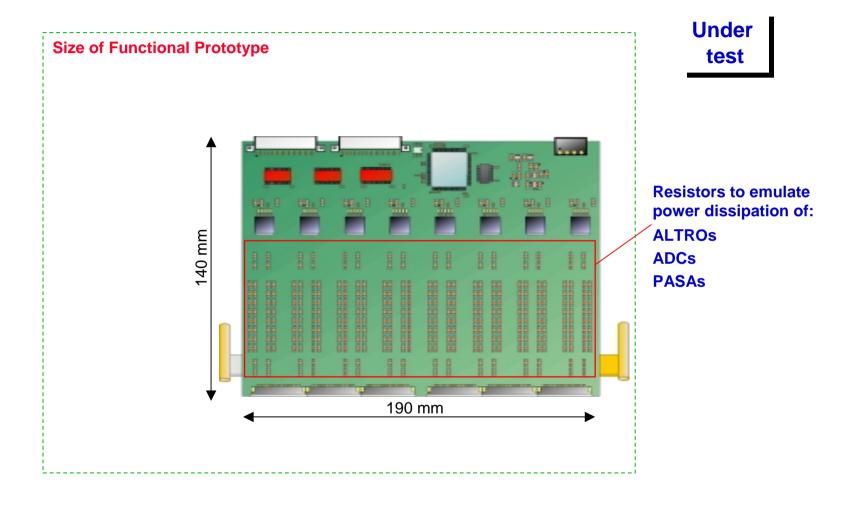

#### **FEC – FUNCTIONAL PROTOTYPE**

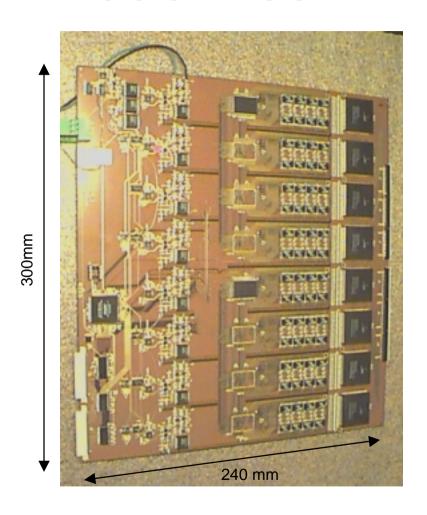

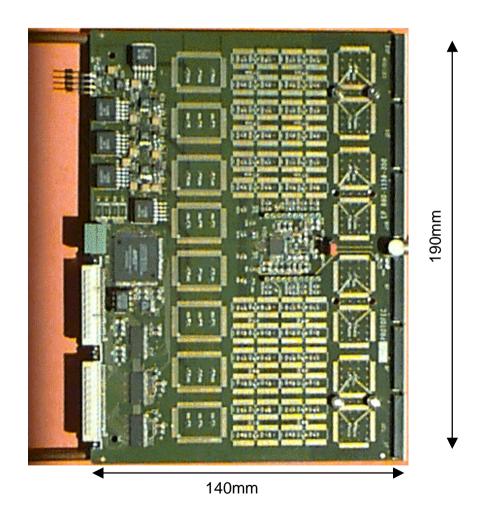

## FRONT-END CARD PROTOTYPES (2001)

#### **FUNCTIONAL PROTOTYPE**

#### **LIGHT PROTOTYPE**

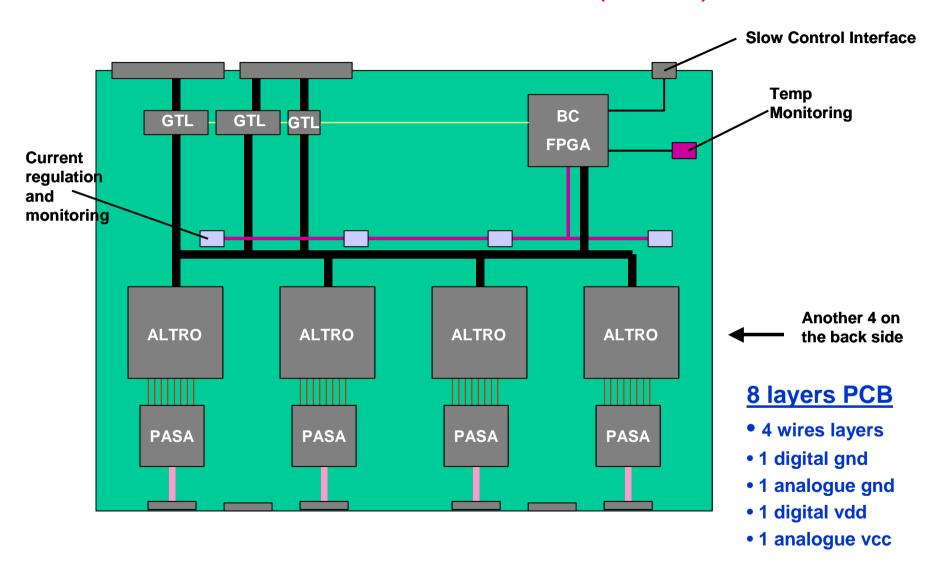

### **NEW FRONT-END CARD PROTOTYPE (FEB 2002)**

A-side

# **FEC INTERNAL BUS** 4 pF GTL 4.7 cm 2 cm **FPGA** BD4CR **B-side** 5 cm

#### **FUTURE WORK**

- Optimization of the FEC internal data bus

- Selection of the technology for the implementation of the board controller:

- SRAM FPGA (ALTERA) vs. anti-fuse FPGA (ACTEL)

- Hardcopy FPGA (ALTERA)

- Hardwired gate array (two masks technology)

- Design, implementation and test of the local slow control bus

- Test of the distribution of the clock signals (sampling clock and readout clock) and write a proposal:

- Bus line vs. point-to-point connection

- distribution of a single clock line (40 MHz) and generation of the sampling clock in the RCU by the use of PLL, or distribution of two independent clock lines?

- Define a scheme for a bulky electrical connection of the FEC ground to the ROC frame